- 您现在的位置:买卖IC网 > Sheet目录1991 > CS43L22-CNZR (Cirrus Logic Inc)IC DAC W/HDPN & SPKR AMPS 40-QFN

DS792F2

17

CS43L22

Confidential Draft

3/4/10

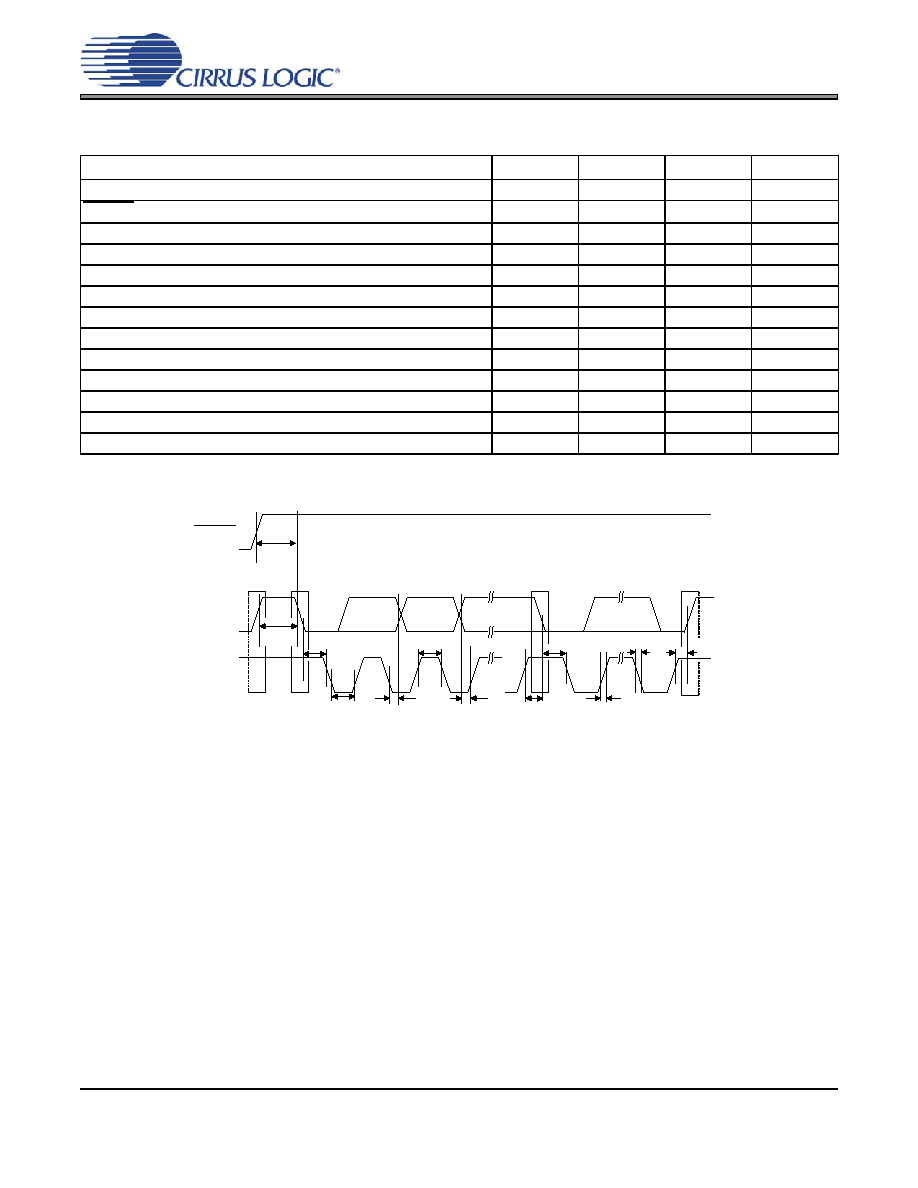

SWITCHING SPECIFICATIONS - IC CONTROL PORT

Inputs: Logic 0 = DGND; Logic 1 = V; SDA CL =30pF.

13. Data must be held for sufficient time to bridge the transition time, tfc, of SCL.

Parameters

Symbol

Min

Max

Unit

SCL Clock Frequency

fscl

-

100

kHz

RESET Rising Edge to Start

tirs

550

-

ns

Bus Free Time Between Transmissions

tbuf

4.7

-

s

Start Condition Hold Time (prior to first clock pulse)

thdst

4.0

-

s

Clock Low time

tlow

4.7

-

s

Clock High Time

thigh

4.0

-

s

Setup Time for Repeated Start Condition

tsust

4.7

-

s

SDA Hold Time from SCL Falling

thdd

0-

s

SDA Setup time to SCL Rising

tsud

250

-

ns

Rise Time of SCL and SDA

trc

-1

s

Fall Time SCL and SDA

tfc

-

300

ns

Setup Time for Stop Condition

tsusp

4.7

-

s

Acknowledge Delay from SCL Falling

tack

300

1000

ns

t

buf

t

hdst

t

hdst

t

low

t r

t f

t

hdd

t

high

t sud

t sust

t susp

Stop

Start

Stop

Repeated

SDA

SCL

t

irs

RESET

Figure 4. Control Port Timing - IC

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

CS4461-CZZR

IC ADC PSR FEEDBACK 24-TSSOP

CS5340-CZZ

IC ADC AUD 101DB 200KHZ 16-TSSOP

CS5340-DZZR

IC ADC AUD 101DB 200KHZ 16-TSSOP

CS5341-DZZ

IC ADC AUD 105DB 200KHZ 16-TSSOP

CS5342-CZZ

IC ADC AUD 105DB 200KHZ 16-TSSOP

CS5345-CQZ

IC ADC AUD 104DB 200KHZ 48-LQFP

CS5345-DQZ

IC ADC AUD 104DB 200KHZ 48-LQFP

CS5346-CQZR

IC ADC AUD 103DB 200KHZ 48-LQFP

相关代理商/技术参数

CS43L23-CWZR

功能描述:IC DAC W/HDPN & SPKR AMPS 40-QFN 制造商:cirrus logic inc. 系列:* 零件状态:Not For New Designs 标准包装:6,000

CS43L36-CNZ

功能描述:IC-LOWPOWERHIGHPERFORMANCE HEADP 制造商:cirrus logic inc. 系列:* 零件状态:在售 标准包装:490

CS43L41

制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:Low Power 24-Bit, 96 kHz DAC with Volume Control

CS43L41-KZ

制造商:Rochester Electronics LLC 功能描述:- Bulk

CS43L42

制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:Low Voltage,Stereo DAC With Headphone Amp

CS43L42-EP

制造商:Cirrus Logic 功能描述:

CS43L42-KZ

功能描述:数模转换器- DAC IC Low PWR Str DAC w/Hdphn & Line Amp RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube

CS43L42-KZR

功能描述:数模转换器- DAC IC Low PWR Str DAC w/Hdphn & Line Amp RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube